UCIe 3.0 Verification IP

Truechip's UCIe Verification IP offers a streamlined and efficient solution for verifying UCIe components within an IP or SoC. Truechip's VIP fully adheres to the UCIe Specification version 3.0 and features a lightweight, plug-and-play design, ensuring that it does not impact the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure the highest levels of quality.

- Availability of various Regression Test Suites.

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components.

- Consistency of interface, installation, operation, and documentation across all our VIPs.

- Provide complete solutions and easy integration in IP and SoC environments.

Features

- Natively maps PCI Express (PCIe 6.0) and Compute Express Link (CXL 2.0, CXL 3.0) protocols.

- Supports CXL 2.0 68B Flit Mode, CXL 256B Flit Mode, PCIe 6.0 Flit Mode and Raw Mode for all protocols.

- Supports streaming protocol for Raw format.

- Supports AXI 3 & 4 Protocols using Raw format.

- Supports Management Transport Protocol for Raw mode and all 256B flit format.

- Supports standard (2D), Advanced package (2.5D) and UCIe-3D.

- Supports single module, two module and four module configurations.

- Supports sideband-only configuration for 1,2 and 4 sideband-only port.

- Supports up to 64 GT/s per pin including 48 GT/s and 64 GT/s data rates (4 GT/s for 3D Packaging).

- Available with 8/16/32 and 64 lanes.

- Supports lane reversal.

- Supports lane repair (advanced) and link width degradation (standard).

- Supports Flow control and Retry mechanism.

- Supports runtime Link Testing through Parity, Scrambling/De-scrambling.

- Supports all types of sideband messages, including new priority sideband packets.

- Supports LTSM, RDI state machine and FDI state machine.

- Supports single and multiple CXL stacks with internal ARB/MUX layer.

- Available with in-built UCIe Retimers.

- Provides functional coverage for complete UCIe features.

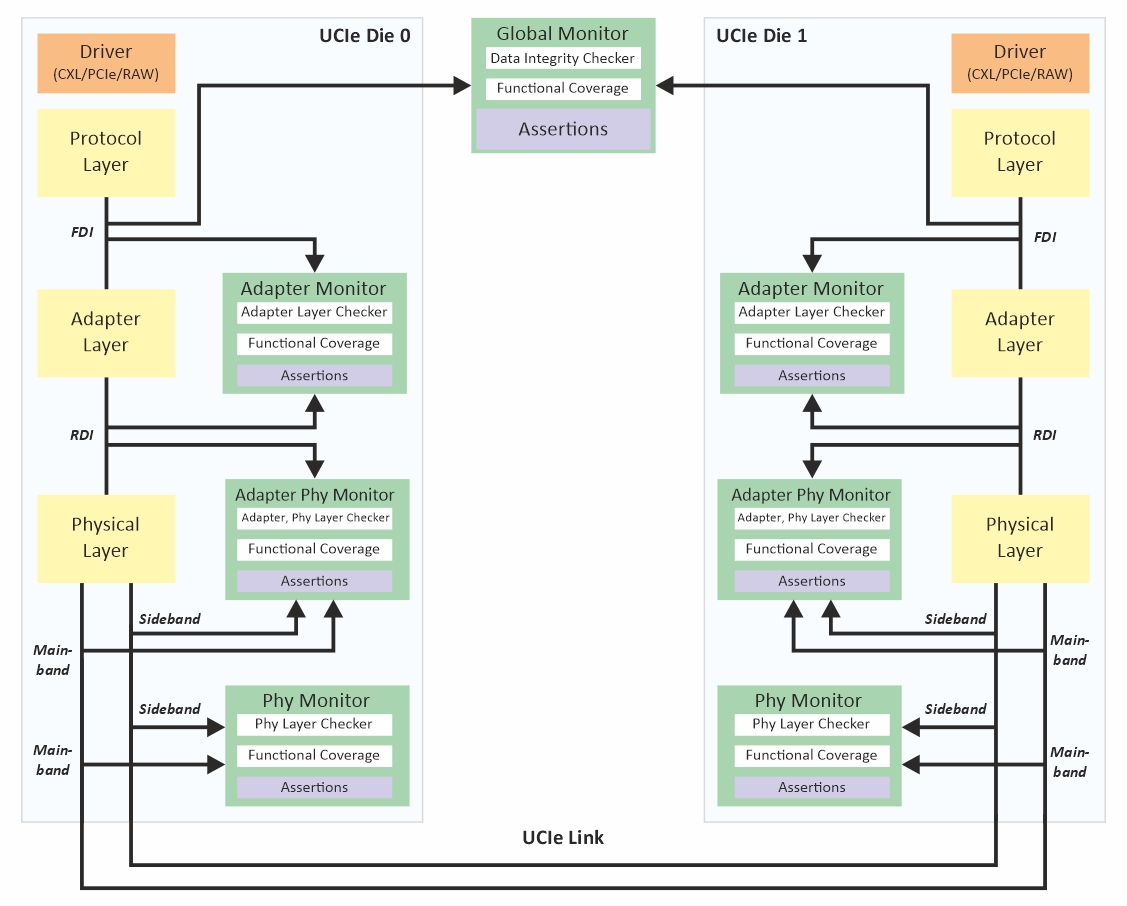

- Monitors detect and notify the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Supports runtime recalibration for enhanced power efficiency.

- Supports power management across different layers, with L2 state optimization.

- Includes fast throttle and emergency shutdown mechanisms via open-drain I/O.

- Compatible with UCIe Manageability, UDA(UCIe Debug and test architecture) and MTP(Management Transport Packet) Encapsulation.

Deliverables

- UCIe Tx/Rx/BFM/Agent

- UCIe Monitor

- UCIe Scoreboard

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests & Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes